Что такое Радиосвязь

Радиосвязь, электросвязь посредством радиоволн. Для осуществления Радиосвязи в пункте, из которого ведётся передача сообщений (радиопередача), размещают радиопередающее устройство, содержащее радиопередатчик и передающую антенну, а в пункте, в котором ведётся приём сообщений (радиоприём), - радиоприёмное устройство, содержащее приёмную антенну и радиоприёмник. Генерируемые в передатчике гармонические колебания с несущей частотой, принадлежащей какому-либо диапазону радиочастот (см. Радиоволны), подвергаются модуляции в соответствии с передаваемым сообщением (см. Модуляция колебаний). Модулированные радиочастотные колебания представляют собой радиосигнал. От передатчика радиосигнал поступает в передающую антенну, посредством которой в окружающем антенну пространстве возбуждаются соответственно модулированные электромагнитные волны. Распространяясь, радиоволны достигают приёмной антенны и возбуждают в ней электрические колебания, которые поступают далее в радиоприёмник. Принятый т. о. радиосигнал очень слаб, т.к. в приёмную антенну попадает лишь ничтожная часть излученной энергии (см. Распространение радиоволн). Поэтому радиосигнал в радиоприёмнике поступает в электронный усилитель, после чего он подвергается демодуляции, или детектированию; в результате выделяется сигнал, аналогичный сигналу, которым были модулированы колебания с несущей частотой в радиопередатчике. Далее этот сигнал (обычно дополнительно усиленный) преобразуется при помощи соответствующего воспроизводящего устройства в сообщение, адекватное исходному.

В месте приёма на радиосигнал могут накладываться электромагнитные колебания от посторонних источников радиоизлучений, способные помешать правильному воспроизведению сообщения и называемые поэтому помехами радиоприёму. Неблагоприятное влияние на качество радиосвязи могут оказывать также изменение во времени затухания радиоволн на пути распространения от передающей антенны к приёмной (см. Замирания) и распространение радиоволн одновременно по двум или нескольким траекториям различной протяжённости; в последнем случае электромагнитное поле в месте приёма представляет собой сумму взаимно смещенных во времени радиоволн, интерференция которых также вызывает искажения радиосигнала. Поэтому и эти явления относят к категории помех радиоприёму. Их влияние на приём радиосигналов особенно велико при связи на больших расстояниях. Широкое распространение радиосвязи и использование радиоволн в радиолокации, радионавигации и др. областях техники потребовали обеспечения одновременного функционирования без недопустимых взаимных помех различных систем и средств, использующих радиоволны, - обеспечения их электромагнитной совместимости.

Распространение радиоволн в открытом пространстве делает возможным в принципе приём радиосигналов, передаваемых по линиям радиосвязи, лицами, для которых они не предназначены (радиоперехват, радиоподслушивание); в этом - недостаток радиосвязи по сравнению с электросвязью по кабелям, радиоволноводам и др. закрытым линиям. Тайна телефонных переговоров и телеграфных сообщений, предусматриваемая уставом связи СССР, соответствующими правилами др. стран и международными соглашениями, обеспечивается в необходимых случаях применением автоматических средств засекречивания радиосигналов (кодирование и др.).

Попытки осуществить радиосвязь предпринимал ещё Т. А. Эдисон в 80-е гг. 19 в. (им получен соответствующий патент), до открытия в 1888 электромагнитных волн Г. Герцем;хотя работы Эдисона не имели практического успеха, они способствовали появлению др. работ, направленных на реализацию идеи беспроводной связи. Герцем был создан искровой излучатель электромагнитных волн, который (с последующими различными усовершенствованиями) в течение нескольких десятилетий оставался наиболее распространённым в радиосвязи видом радиопередатчика. Возможность и основные принципы радиосвязи были подробно описаны У. Круксом в 1892, но в то время ещё не предвиделось скорой реализации этих принципов. Развитие радиосвязи началось после того, как в 1895 А. С. Поповым,а годом позже Г. Маркони были созданы чувствительные приёмники, вполне пригодные для осуществления сигнализации без проводов, т. е. для радиосвязи. Первая публичная демонстрация Поповым работы созданной им радиоаппаратуры и беспроводной передачи сигналов с её помощью состоялась 7 мая 1895, что даёт основание считать эту дату фактическим днём появления Радиосвязи.

Приёмник Попова не только оказался пригодным для радиосвязи, но и (с некоторыми дополнительными узлами) был впервые успешно применен им в том же 1895 для автоматической записи грозовых разрядов, чем было положено начало радиометеорологии. В странах Западной Европы и США была развёрнута активная деятельность по использованию радиосвязи в коммерческих целях. Маркони в 1897 зарегистрировал в Англии Компанию беспроводного телеграфирования и сигнализации, в 1899 основал Американскую компанию беспроводной и телеграфной связи, а в 1900 - Международную компанию морской связи. В декабре 1901 им была осуществлена радиотелеграфная передача через Атлантический океан. В 1902 в Германии производство оборудования для радиосвязи организовал А. Слаби (совместно с Г. Арко), а также К. Ф. Браун. Очевидное огромное значение радиосвязи для военных флотов и для морского транспорта, а также гуманистическая роль радиосвязи (при спасании людей с кораблей, потерпевших крушение) стимулировали развитие её во всём мире. На 1-й Международной административной конференции в Берлине в 1906 с участием представителей 29 стран были приняты регламент радиосвязи и международная конвенция, вступившая в силу с 1 июля 1908. В регламенте было зафиксировано распределение радиочастот между разными службами радиосвязи (см. ниже). Было основано Бюро регистрации радиостанций и установлен международный сигнал бедствия SOS. На международной конференции в Лондоне в 1912 было несколько изменено распределение частот, уточнён регламент и учреждены новые службы: радиомаячная, передачи сводок погоды и передачи сигналов точного времени. По решению радиоконференции 1927 было запрещено применение искровых радиопередатчиков, создававших излучение в широком спектре частот и препятствовавших тем самым эффективному использованию радиочастот; искровые передатчики были оставлены только для передачи сигналов бедствия, поскольку широкий спектр излучения радиоволн увеличивает вероятность их приёма. С 1915 до 50-х гг. аппаратура для радиосвязи развивалась главным образом на основе электронных ламп; затем были внедрены транзисторы и др. полупроводниковые приборы.

До 1920 в радиосвязь применялись преимущественно волны длиной от сотен м до десятков км. В 1922 радиолюбителями было открыто свойство декаметровых (коротких) волн распространяться на любые расстояния благодаря преломлению в верхних слоях атмосферы и отражению от них. Вскоре такие волны стали основным средством осуществления дальней радиосвязи Для приёма передаваемых т. о. сигналов, приходящих с больших расстояний, служат чувствительные приёмники и большие, сравнительно остронаправленные антенные сооружения, занимающие большую территорию, т. н. антенное поле (подобные же сооружения используются и для излучения декаметровых волн). Для ослабления радиопомех приёмное оборудование размещается в стороне от городов и вдали от радиопередатчиков, на специальных приёмных радиоцентрах. Радиопередающие устройства также группируются - на передающих радиоцентрах. Те и другие связаны с находящимся в городе центральным телеграфом, откуда поступают передаваемые и куда транслируются принимаемые сигналы.

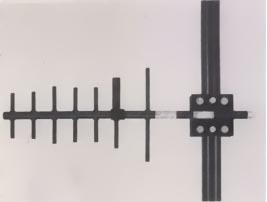

В 30-е гг. были освоены метровые, а в 40-е - дециметровые и сантиметровые волны, распространяющиеся в основном прямолинейно, не огибая земной поверхности (т. е. в пределах прямой видимости), что ограничивает прямую связь на этих волнах расстоянием в 40-50 км. Поскольку ширина диапазонов частот, соответствующих этим длинам волн, - от 30 Мгц до 30 Ггц - в 1000 раз превышает ширину всех диапазонов частот ниже 30 Мгц (волны длиннее 10 м), то они позволяют передавать огромные потоки информации, осуществляя многоканальную связь. В то же время ограниченная дальность распространения и возможность получения острой направленности с антенной несложной конструкции позволяют использовать одни и те же длины волн во множестве пунктов без взаимных помех. Передача на значительные расстояния достигается применением многократной ретрансляции в линиях радиорелейной связи или с помощью спутников связи, находящихся на большой высоте (около 40 тыс. км) над Землёй (см. Космическая связь). Позволяя вести на больших расстояниях одновременно десятки тысяч телефонных разговоров и передавать десятки телевизионных программ, радиорелейная и спутниковая связь по своим возможностям являются несравненно более эффективными, чем обычная дальняя радиосвязь на декаметровых волнах, значимость которой соответственно уменьшается (за ней, например, остаётся роль полезного резерва, а также роль средства связи на направлениях с малыми потоками информации).

При большой мощности радиопередатчика (десятки квт) радиосвязь на метровых волнах в узкой полосе частот (несколько кгц) возможна на расстояниях ~ 1000 км за счёт рассеяния волн в ионосфере (см. Ионосферная радиосвязь). Пользуются также отражением радиоволн от ионизованных следов метеоров, сгорающих в верхних слоях атмосферы (см. Метеорная радиосвязь), но при этом передача информации идёт с перерывами, что не позволяет осуществлять телефонных переговоры.

Малая часть энергии излучения на дециметровых и сантиметровых волнах может также распространяться за пределы горизонта (на расстояния в сотни км) благодаря электрической неоднородности тропосферы. Это позволяет при сравнительно большой мощности передатчиков (порядка нескольких квт) строить линии радиорелейной связи с расстоянием между промежуточными станциями в 200-300 км и более (при сужении частотного спектра излучения, т. е. уменьшении объёма передаваемой информации, см. Тропосферная радиосвязь).

Линии радиосвязи используются для передачи телефонных сообщений, телеграмм, потоков цифровой информации и факсимиле, а также и для передачи телевизионных программ (обычно на метровых и более коротких волнах). По назначению и дальности действия различают международные и внутрисоюзные общегосударственные линии радиосвязи. Внутрисоюзные линии делятся на магистральные (между столицей СССР и столицами союзных республик, краевыми и областными центрами, а также между последними) и зоновые (внутриобластные и внутрирайонные). Развитие линий радиосвязи планируется с учётом вхождения радиосвязи в Единую автоматизированную систему связи страны.

Организационно-технические мероприятия и средства для установления радиосвязи и обеспечения её систематического функционирования образуют службы радиосвязи, различаемые по назначению, дальности действия, структуре и др. признакам. В частности, существуют службы: наземной и космической радиосвязи (к космической радиосвязи относят все виды радиосвязи с использованием одного или нескольких спутников или иных космических объектов); фиксированной (между определёнными пунктами) и подвижной (между подвижной и стационарной радиостанциями или между подвижными радиостанциями); радиовещания и телевидения. Для производственных и специальных служебных надобностей имеются ведомственные службы радиосвязи в некоторых министерствах и организациях (например, в гражданской авиации, на ж.-д., морском и речном транспорте, в службах пожарной охраны, милиции, медицинской службе городов), а также внутрипроизводственная связь на промышленных и с.-х. предприятиях, в некоторых учреждениях и т.д. (см. также Радиостанция низовой связи). Большое значение имеет радиосвязь в вооружённых силах.

Информация взята из сайта http://www.raciiru.ru/history/